# 1/2.6-inch 2.3 Mp CMOS **Digital Image Sensor** with Global Shutter

## AR0234CS

#### Description

The AR0234CS is a 1/2.6-inch 2Mp CMOS digital image sensor with an active-pixel array of 1920 (H) x 1200 (V). It incorporates a new innovative global shutter pixel design optimized for accurate and fast capture of moving scenes at full resolution 120 frame per second. The sensor produces clear, low noise images in both low-light and bright scenes. It includes sophisticated camera functions such as auto exposure control, windowing, row skip mode, column-skip mode, pixel-binning and both video and single frame modes. It is programmable through a simple two-wire serial interface. The AR0234CS produces extraordinarily clear, sharp digital pictures with an industry leading Global Shutter Efficiency, and its ability to capture both continuous video and single frames makes it the perfect choice for a wide range of applications, including scanning and industrial inspection.

**Table 1. KEY PERFORMANCE PARAMETERS**

| Parameter                                  | Typical Value                                                                                                         |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Optical Format                             | 1/2.6–inch (6.8 mm)                                                                                                   |

| Active Pixels                              | 1920 (H) x 1200 (V) = 2.3 Mp                                                                                          |

| Pixel Size                                 | 3.0 µm                                                                                                                |

| Color Filter Array                         | RGB or Monochrome                                                                                                     |

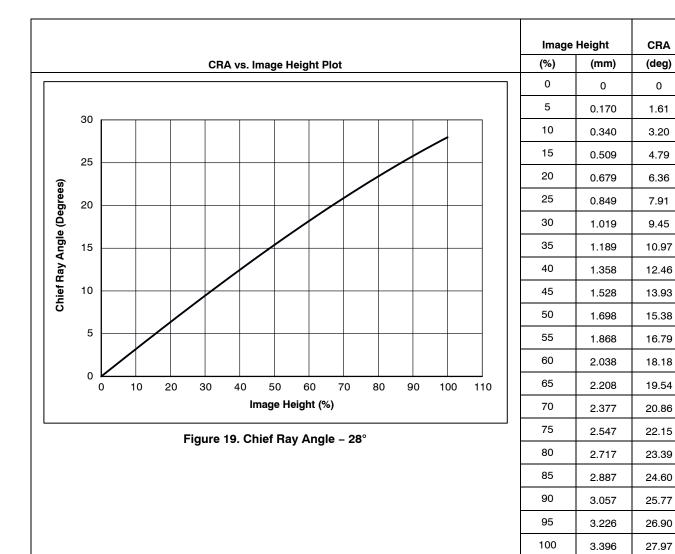

| Chief Ray Angle                            | 0° or 28°                                                                                                             |

| Shutter Type                               | Global Shutter                                                                                                        |

| Input Clock Range                          | 6–54 MHz                                                                                                              |

| Output Pixel Clock<br>(Maximum)            | 90 MHz                                                                                                                |

| Output<br>Serial                           | 8-bit/10-bit MIPI, 1, 2, or 4-lane D-<br>PHY 1.2, CSI-2                                                               |

| Parallel                                   | 8-bit/10-Bit                                                                                                          |

| Frame Rate Full resolution 720p            | 120fps (4- lane MIPI running at 30 fps<br>per MIPI lane), Default<br>Max data rate 900 Mbps/lane<br>30 fps (Parallel) |

| 7256                                       | 120 fps (MIPI)<br>50 fps (Parallel)                                                                                   |

| Responsivity<br>Monochrome<br>Color        | 55 Ke/lux*s<br>TBD                                                                                                    |

| SNRMAX                                     | 37 dB                                                                                                                 |

| Dynamic Range                              | 70 dB                                                                                                                 |

| Supply Voltage<br>I/O<br>Digital<br>Analog | 1.8 or 2.8 V<br>1.2 V<br>2.8 V                                                                                        |

| Operational Power Consumption              | <420 mW                                                                                                               |

| Operating Temperature                      | -40°C to + 85°C (Ambient)<br>-40°C to +105°C (Junction)                                                               |

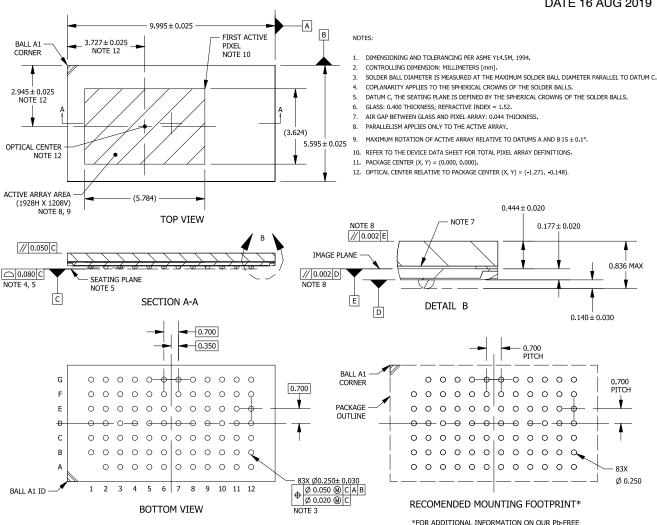

| Package Options                            | 9.995 x 5.595 CSP                                                                                                     |

## ON Semiconductor®

www.onsemi.com

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

#### **Features**

- Superior Low-light and IR Performance

- HD Video (1080p120)

- 8-bit/10-bit MIPI, 1/2/4-lane MIPI or 8-bit/10-bit Parallel Data Interface

- Automatic Black Level Calibration (ABLC)

- On-chip Auto Exposure Control with Statistics Engine for Any 5x5 Programmable ROI

- Horizontal and Vertical Mirroring, Windowing and Pixel Binning

- On-chip Histogram Auto Exposure Control for Any Programmable ROI

- 5 x 5 Statistics Engine for Any Programmable ROI

- Flexible Control for Row and Column Skip

- On-chip Slave or Trigger Mode for Synchronization

- Built in Strobe Control

- On-Chip Phase Lock Loop (PLL)

- On-Chip Lens Shading Correction

This document, and the information contained herein, is CONFIDENTIAL AND PROPRIETARY and the property of Semiconductor Components Industries, LLC., dba ON Semiconductor. It shall not be used, published, disclosed or disseminated outside of the Company, in whole or in part, without the written permission of ON Semiconductor. Reverse engineering of any or all of the information contained herein is strictly prohibited.

© 2017, SCILLC. All Rights Reserved.

# CONFIDENTIAL AND PROPRIETARY NOT FOR PUBLIC RELEASE

## **AR0234CS**

#### **Applications**

- Bar Code Scanner

- Gesture Recognition

- 3D Scanning

- Positional Tracking

- Iris Scanning

- Augmented Reality

- Virtual Reality

- Biometrics

- Machine Vision

#### ORDERING INFORMATION

**Table 2. AVAILABLE PART NUMBERS**

| Part Number             | Product Description            | Orderable Product Attribute Description                 |

|-------------------------|--------------------------------|---------------------------------------------------------|

| AR0234CSSM28SUKA0-CP    | 2.3MP 1/2.6", Mono, 28 deg CRA | CSP Chip Tray with Protective Film                      |

| AR0234CSSM28SUKA0-CR    | 2.3MP 1/2.6", Mono, 28 deg CRA | CSP Chip Tray without Protective Film                   |

| AR0234CSSM28SUKA0-CP1   | 2.3MP 1/2.6", Mono, 28 deg CRA | CSP Chip Tray with Protective Film Low MOQ              |

| AR0234CSSM28SUKA0-CR1   | 2.3MP 1/2.6", Mono, 28 deg CRA | CSP Chip Tray without Protective Film Low MOQ           |

| AR0234CS3M28SUD20-E     | 2.3MP 1/2.6", Mono, 28 deg CRA | Bare Die, Engineering Samples                           |

| AR0234CSSM28SUKAH3-GEVB | 2.3MP 1/2.6", Mono, 28 deg CRA | Demo Headboard                                          |

| AR0234CS3M00SUKA0-CP-E  | 2.3MP 1/2.6", Mono, 0 deg CRA  | CSP Chip Tray with Protective Film, Engineering Samples |

| AR0234CS3M00SUD20-E     | 2.3MP 1/2.6", Mono, 0 deg CRA  | Bare Die, Engineering Samples                           |

| AR0234CSSM00SUKAH3-GEVB | 2.3MP 1/2.6", Mono, 0 deg CRA  | Demo Headboard                                          |

| AR0234CS3C28SUKA0-CP-E  | 2.3MP 1/2.6", RGB, 28 deg CRA  | CSP Chip Tray with Protective Film, Engineering Samples |

| AR0234CS3C28SUD20-E     | 2.3MP 1/2.6", RGB, 28 deg CRA  | Bare Die, Engineering Samples                           |

| AR0234CSSC28SUKAH3-GEVB | 2.3MP 1/2.6", RGB, 28 deg CRA  | Demo Headboard                                          |

| AR0234CS3C00SUKA0-CP-E  | 2.3MP 1/2.6", RGB, 0 deg CRA   | CSP Chip Tray with Protective Film, Engineering Samples |

| AR0234CS3C00SUD20-E     | 2.3MP 1/2.6", RGB, 0 deg CRA   | Bare Die, Engineering Samples                           |

| AR0234CSSC00SUKAH3-GEVB | 2.3MP 1/2.6", RGB, 0 deg CRA   | Demo Headboard                                          |

NOTE: Please check with an ON Semiconductor sales representative for availability of these parts.

#### **GENERAL DESCRIPTION**

The ON Semiconductor AR0234CS can be operated in its default mode or programmed for frame size, exposure, gain, and other parameters. The default mode output is a full–resolution image at 120 frames per second (fps). It outputs 8-bit or 10-bit raw data using parallel output ports or 10-bit or 8-bit using serial (MIPI) output ports. The device may be operated in video (master) mode or in frame trigger mode.

FRAME\_VALID and LINE\_VALID signals are output on dedicated pins, along with a synchronized pixel clock. A dedicated FLASH pin can be programmed to control external LED or flash exposure illumination.

The AR0234CS includes additional features to allow application-specific tuning: windowing, adjustable

auto-exposure control, auto black level correction, on-board temperature sensor, row-skip and column-skip modes and binning modes.

The sensor is designed to operate in a wide ambient temperature range (-40°C to +85°C ambient).

## **FUNCTIONAL OVERVIEW**

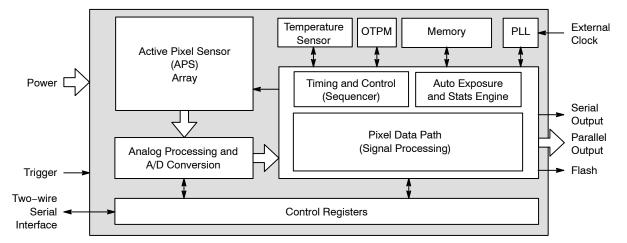

The AR0234CS is a progressive–scan sensor that generates a stream of pixel data at a constant frame rate. It uses an on–chip, phase–locked loop (PLL) that can be optionally enabled to generate all internal clocks from a single master input clock running between 6 and 54 MHz. The maximum output pixel rate is 90 Mp/s, corresponding to a clock rate of 90 MHz. Figure 1 shows a block diagram of the sensor.

Figure 1. Block Diagram

User interaction with the sensor is through the two-wire serial bus, which communicates with the array control, analog signal chain, and digital signal chain. The core of the sensor is a 2.3 Mp Active-Pixel Sensor array. The AR0234CS features global shutter technology for accurate capture of moving images. The exposure of the entire array is controlled by programming the integration time by register setting. All pixels simultaneously integrate light and store signal at the pixel. Once a row readout sequence has been initiated, each pixel's stored signal is then transfered through the analog signal chain (providing offset and gain) and then through each column analog to-digital converter (ADC). The output from the ADC is a 10-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further data path corrections and applies digital gain). The pixel data are output at a rate of up to 90 Mp/s, in parallel to frame and line synchronization signals.

#### **FEATURES OVERVIEW**

The AR0234CS Global Shutter sensor has a wide array of features to enhance functionality and to increase versatility. A summary of features follows.

3.0 μm Global Shutter Pixel

To improve the low light performance and to capture the moving images accurately a large (3.0 μm) global shutter pixel is implemented for better image optimization.

## • Operating Modes

The AR0234CS works in master (video), Slave/Trigger (single frame), or Auto Trigger modes. In master mode, the sensor generates the integration and readout timing. In Slave/trigger mode, it accepts a trigger from external host to start exposure, then generates the exposure and readout timing. The external trigger signal allows for precise control of frame rate and register change updates. The exposure time is programmed through the two-wire serial interface for both modes.

#### Window Control

Configurable window size and blanking times allow a wide range of resolutions and frame rates. Digital binning and skipping modes are supported, as are vertical and horizontal mirror operations.

#### • Frame Rate

AR0234CS is capable of running up to 120 fps at full (1920 x 1200) resolution and 120 fps at 720p resolution for MIPI interface.

- Embedded Data and Statistics

The AR0234CS has the capability to output image data and statistics embedded within the frame timing.

- Multi-Camera Synchronization

The AR0234CS supports advanced line synchronization controls for multi-camera (stereo) support.

- Context Switching and Register Updates Context switching may be used to rapidly switch between two sets of register values.

#### • Gain

A programmable analog gain of 1x to 16x applied globally to all color channels is available for along with a digital gain of 1x to 16x that may be configured on a per color channel basis. Programmable analog gain for Parallel interface is limited to 8x.

#### Automatic Exposure Control

The integrated automatic exposure control may be used to ensure optimal settings of exposure and gain are computed and updated every other frame.

#### MIPI

The AR0234CS Global Shutter image sensor supports one, two and four lanes of MIPI data. Compliant to MIPI standards:

- MIPI Alliance Standard for CSI-2 version 1.2

- MIPI Alliance Standard for D-PHY version 1.0

#### • PLL

An on chip PLL provides reference clock flexibility and

# CONFIDENTIAL AND PROPRIETARY NOT FOR PUBLIC RELEASE

## **AR0234CS**

supports spread spectrum sources for improved EMI performance.

- Reset

- The AR0234CS may be reset by a register write, or by a dedicated input pin.

- Output Enable

- The AR0234CS output pins may be tri-stated using a dedicated output enable pin.

- Temperature Sensor

- Black Level Correction

- Row Noise Correction

- Test Patterns

- Several test patterns may be enabled for debug

- purposes. These include a solid color, color bar, fade to gray, and a walking 1s test pattern.

- Silicon/OTPM Revision Information

A revision register is provided to read out (via I<sup>2</sup>C) silicon and OTPM revision information. This will be helpful to distinguish material if there are future OTPM or silicon revisions.

- Lens Shading Correction

An on-chip lens shading correction algorithm is included

- Compression

AR0234CS can optionally compress 10-bit data to 8-bit using DPCM compression.

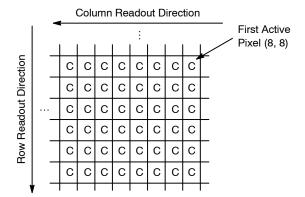

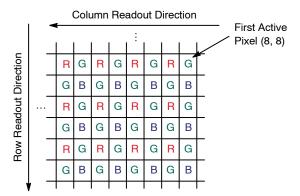

## **ACTIVE ARRAY**

The AR0234CS active pixel array is configured as 1920 columns by 1200 rows. The first active the pixel is top right corner of the active pixel array (see Figures 2 and 3 below).

Figure 2. Pixel Mono Pattern Detail (Top Right Corner)

Figure 3. Pixel Color Pattern Detail (Top Right Corner)

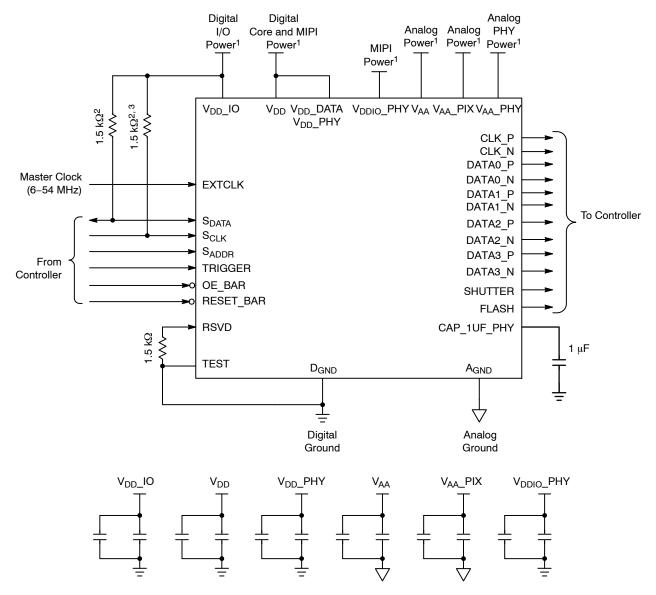

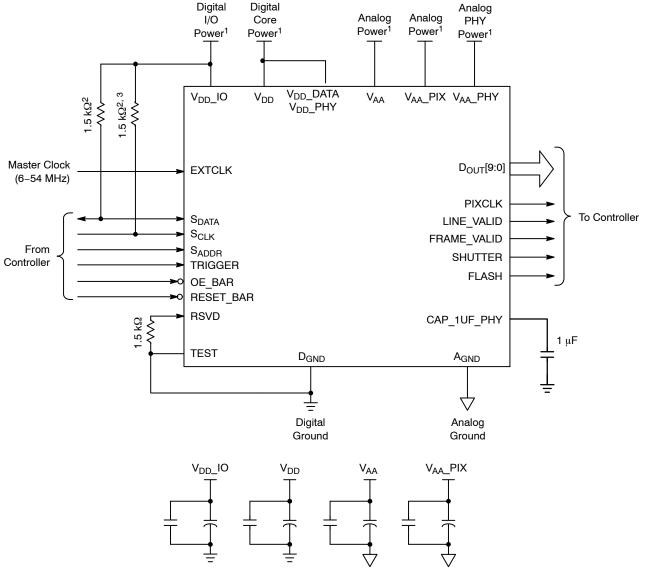

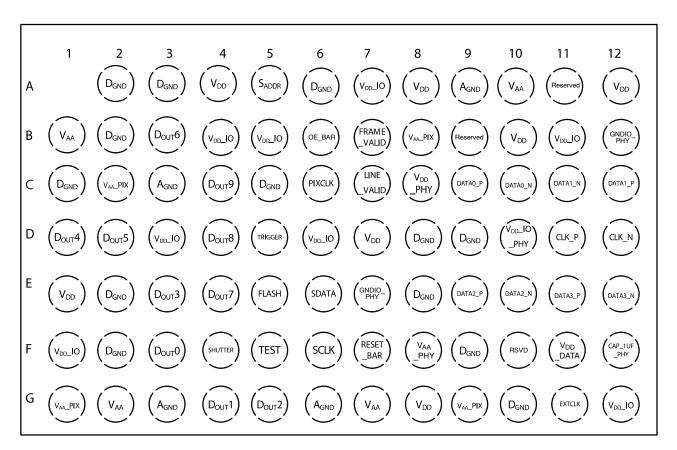

#### **CONFIGURATION AND PINOUT**

The figures and tables below show a typical configuration for the AR0234CS image sensor and show the package pinouts.

#### Notes:

- 1. All power supplies must be adequately decoupled.

- 2. ON Semiconductor recommends a resistor value of 1.5 kΩ, but a greater value may be used for slower two–wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on S<sub>CLK</sub> at all times.

- 4. The parallel interface output pads can be left unconnected if the serial output interface is used.

- 5. Analog and digital grounds need to be connected at a single point.

- 6. ON Semiconductor recommends that  $0.1 \mu F$  and  $10 \mu F$  decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on the layout and design considerations. Refer to the AR0234CS demo headboard schematics for circuit recommendations.

- ON Semiconductor recommends that analog power planes be placed in a manner such that coupling with the digital power planes is minimized.

- 8. It is recommended that VDD PHY and VDD DATA are tied to VDD (1.2 V).

- 9. It is recommended that VAA PHY is connected to 2.8 V.

- 10. VDDIO\_PHY should be connected to 1.8 V only.

Figure 4. Serial 4-lane MIPI Interface

## Notes:

- 1. All power supplies must be adequately decoupled.

- 2. ON Semiconductor recommends a resistor value of 1.5 k $\Omega$ , but a greater value may be used for slower two–wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on S<sub>CLK</sub> at all times.

- 4. The serial interface output pads can be left unconnected if the parallel output interface is used.

- 5. Analog and digital grounds need to be connected at a single point.

- 6. ON Semiconductor recommends that 0.1  $\mu$ F and 10  $\mu$ F decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on the layout and design considerations. Refer to the AR0234CS demo headboard schematics for circuit recommendations.

- 7. ON Semiconductor recommends that analog power planes be placed in a manner such that coupling with the digital power planes is minimized.

- 8. It is recommended that  $V_{DD}$ PHY and  $V_{DD}$ DATA are tied to  $V_{DD}$  (1.2 V).

- 9. It is recommended that VAA\_PHY is connected to 2.8 V.

- 10. VDDIO\_PHY should be connected to 1.8 V only.

Figure 5. Parallel Interface

Figure 6. 9.995 x 5.595 mm 83-ball CSP Package (Top View)

Table 3. PIN DESCRIPTIONS - 83-BALL CSP PACKAGE

| Name                 | CSP Ball                                              | Туре   | Description                                                                    |

|----------------------|-------------------------------------------------------|--------|--------------------------------------------------------------------------------|

| DATA0_N              | C10                                                   | Output | MIPI serial data, lane 0, differential N                                       |

| DATA0_P              | C9                                                    | Output | MIPI serial data, lane 0, differential P                                       |

| DATA1_N              | C11                                                   | Output | MIPI serial data, lane 1, differential N                                       |

| DATA1_P              | C12                                                   | Output | MIPI serial data, lane 1, differential P                                       |

| DATA2_N              | E10                                                   | Output | MIPI serial data, lane 2, differential N                                       |

| DATA2_P              | E9                                                    | Output | MIPI serial data, lane 2, differential P                                       |

| DATA3_N              | E12                                                   | Output | MIPI serial data, lane 3, differential N                                       |

| DATA3_P              | E11                                                   | Output | MIPI serial data, lane 3, differential P                                       |

| CLK_N                | D12                                                   | Output | MIPI serial clock differential N                                               |

| CLK_P                | D11                                                   | Output | MIPI serial clock differential P                                               |

| VAA                  | A10, B1, G2, G7                                       | Power  | Analog Power (2.8 V)                                                           |

| V <sub>AA</sub> _PHY | F8                                                    | Power  | Analog PHY power supply. Analog power supply for the serial interface (2.8 V). |

| EXTCLK               | G11                                                   | Input  | External input clock                                                           |

| VDD_PHY              | C8                                                    | Power  | MIPI Power Supply (1.2 V)                                                      |

| VDDIO_PHY            | D10                                                   | Power  | I/O Power Supply (1.8 V)                                                       |

| DGND                 | A2 A3, A6, B2, C1, C5, D8, D9,<br>E2, E8, F2, F9, G10 | Power  | Digital GND                                                                    |

| GNDIO_PHY            | B12, E7                                               | Power  | Connect to DGND.                                                               |

| VDD                  | A4, A8, A12, B10, D7, E1, G8                          | Power  | Digital Power (1.2 V)                                                          |

Table 3. PIN DESCRIPTIONS - 83-BALL CSP PACKAGE (continued)

| Name                  | CSP Ball                            | Туре   | Description                                                                   |

|-----------------------|-------------------------------------|--------|-------------------------------------------------------------------------------|

| V <sub>DD</sub> _DATA | F11                                 | Power  | MIPI PHY Power (1.2 V)                                                        |

| AGND                  | A9, C3, G3, G6                      | Power  | Analog GND                                                                    |

| SADDR                 | A5                                  | Input  | Two-Wire Serial address select                                                |

| Sclk                  | F6                                  | Input  | Two-Wire Serial clock input                                                   |

| SDATA                 | E6                                  | I/O    | Two-Wire Serial data I/O                                                      |

| VAA_PIX               | B8, C2, G1, G9                      | Power  | Pixel Power (2.8 V)                                                           |

| LINE_VALID            | C7                                  | Output | Asserted when Dout line data is valid                                         |

| FRAME_VALID           | B7                                  | Output | Asserted when DOUT frame data is valid                                        |

| PIXCLK                | C6                                  | Output | Pixel clock out. Dout is valid on rising edge of this clock                   |

| SHUTTER               | F4                                  | Output | Control of external mechanical shutter                                        |

| FLASH                 | E5                                  | Output | Control signal to drive external light sources                                |

| VDD_IO                | A7, B4, B5, B11, D3, D6, F1,<br>G12 | Power  | I/O supply power (1.8 V or 2.8 V)                                             |

| Dout7                 | E4                                  | Output | Parallel pixel data output                                                    |

| <b>D</b> оит8         | D4                                  | Output | Parallel pixel data output                                                    |

| Dоит9                 | C4                                  | Output | Parallel pixel data output (MSB)                                              |

| TEST                  | F5                                  | Input  | Manufacturing test enable pin (connect to DGND)                               |

| Dout4                 | D1                                  | Output | Parallel pixel data output                                                    |

| Dоит5                 | D2                                  | Output | Parallel pixel data output                                                    |

| <b>D</b> оит6         | B3                                  | Output | Parallel pixel data output                                                    |

| TRIGGER               | D5                                  | Input  | Exposure synchronization input                                                |

| OE_BAR                | B6                                  | Input  | Output enable (active LOW). This pin is used for MIPI interface only.         |

| Dout0                 | F3                                  | Output | Parallel pixel data output (LSB)                                              |

| Dout1                 | G4                                  | Output | Parallel pixel data output                                                    |

| Dout2                 | G5                                  | Output | Parallel pixel data output                                                    |

| Dout3                 | E3                                  | Output | Parallel pixel data output                                                    |

| RSVD                  | F10                                 | Input  | Must be connected with 1.5 $k\Omega$ resistor between this pin and DGND.      |

| RESET_BAR             | F7                                  | Input  | Asynchronous reset (active LOW). All settings are restored to factory default |

| CAP_1UF_PHY           | F12                                 | Power  | External bypass capacitor for MIPI Regulator                                  |

| Reserved              | A11, B9                             | N/A    | Reserved (do not connect)                                                     |

#### TWO-WIRE SERIAL REGISTER INTERFACE

The two-wire serial interface bus enables read/write access to control and status registers within the AR0234CS.

The interface protocol uses a master/slave model in which a master controls one or more slave devices. The sensor acts as a slave device. The master generates a clock ( $S_{CLK}$ ) that is an input to the sensor and is used to synchronize transfers. Data is transferred between the master and the slave on a bidirectional signal ( $S_{DATA}$ ).  $S_{DATA}$  is pulled up to  $V_{DD}$ IO off-chip by a 1.5 k $\Omega$  resistor. Either the slave or master device can drive  $S_{DATA}$  LOW – the interface protocol determines which device is allowed to drive  $S_{DATA}$  at any given time.

The protocols described in the two-wire serial interface specification allow the slave device to drive  $S_{CLK}$  LOW; the AR0234CS uses  $S_{CLK}$  as an input only and therefore never drives it LOW.

#### **Protocol**

Data transfers on the two-wire serial interface bus are performed by a sequence of low-level protocol elements:

- a (repeated) start condition

- a slave address/data direction byte

- an (a no) acknowledge bit

- a message byte

- a stop condition

The bus is idle when both  $S_{CLK}$  and  $S_{DATA}$  are HIGH. Control of the bus is initiated with a start condition, and the bus is released with a stop condition. Only the master can generate the start and stop conditions.

#### Start Condition

A start condition is defined as a HIGH-to-LOW transition on  $S_{DATA}$  while  $S_{CLK}$  is HIGH. At the end of a transfer, the master can generate a start condition without previously generating a stop condition; this is known as a "repeated start" or "restart" condition.

## Stop Condition

A stop condition is defined as a LOW-to-HIGH transition on  $S_{DATA}$  while  $S_{CLK}$  is HIGH.

#### Data Transfer

Data is transferred serially, 8 bits at a time, with the MSB transmitted first. Each byte of data is followed by an acknowledge bit or a no-acknowledge bit. This data transfer mechanism is used for the slave address/data direction byte and for message bytes.

One data bit is transferred during each  $S_{CLK}$  clock period.  $S_{DATA}$  can change when  $S_{CLK}$  is LOW and must be stable while  $S_{CLK}$  is HIGH.

#### Slave Address/Data Direction Byte

Bits [7:1] of this byte represent the device slave address and bit [0] indicates the data transfer direction. A "0" in

bit [0] indicates a WRITE, and a "1" indicates a READ. The default slave addresses used by the AR0234CS are 0x20 (write address) and 0x21 (read address) in accordance with the specification. Alternate slave addresses of 0x30 (write address) and 0x31 (read address) can be selected by enabling and asserting the  $S_{\rm ADDR}$  input.

An alternate slave address can also be programmed through R0x31FC.

## Message Byte

Message bytes are used for sending register addresses and register write data to the slave device and for retrieving register read data.

#### Acknowledge Bit

Each 8-bit data transfer is followed by an acknowledge bit or a no-acknowledge bit in the  $S_{CLK}$  clock period following the data transfer. The transmitter (which is the master when writing, or the slave when reading) releases  $S_{DATA}$ . The receiver indicates an acknowledge bit by driving  $S_{DATA}$  LOW. As for data transfers,  $S_{DATA}$  can change when  $S_{CLK}$  is LOW and must be stable while  $S_{CLK}$  is HIGH.

#### No-Acknowledge Bit

The no-acknowledge bit is generated when the receiver does not drive S<sub>DATA</sub> LOW during the S<sub>CLK</sub> clock period following a data transfer. A no-acknowledge bit is used to terminate a read sequence.

#### **Typical Sequence**

A typical READ or WRITE sequence begins by the master generating a start condition on the bus. After the start condition, the master sends the 8-bit slave address/data direction byte. The last bit indicates whether the request is for a read or a write, where a "0" indicates a write and a "1" indicates a read. If the address matches the address of the slave device, the slave device acknowledges receipt of the address by generating an acknowledge bit on the bus.

If the request was a WRITE, the master then transfers the 16-bit register address to which the WRITE should take place. This transfer takes place as two 8-bit sequences and the slave sends an acknowledge bit after each sequence to indicate that the byte has been received. The master then transfers the data as an 8-bit sequence; the slave sends an acknowledge bit at the end of the sequence. The master stops writing by generating a (re)start or stop condition.

If the request was a READ, the master sends the 8-bit write slave address/data direction byte and 16-bit register address, the same way as with a WRITE request. The master then generates a (re)start condition and the 8-bit read slave address/data direction byte, and clocks out the register data, eight bits at a time. The master generates an acknowledge bit after each 8-bit transfer. The slave's internal register address is automatically incremented after every 8 bits are transferred. The data transfer is stopped when the master sends a no-acknowledge bit.

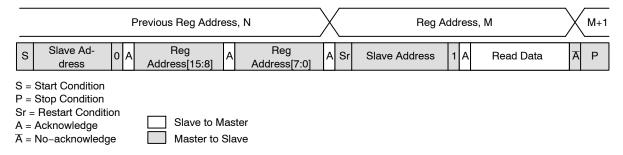

#### Single READ from Random Location

This sequence (Figure 7) starts with a dummy WRITE to the 16-bit address that is to be used for the READ. The master terminates the WRITE by generating a restart condition. The master then sends the 8-bit read slave address/data direction byte and clocks out one byte of

register data. The master terminates the READ by generating a no-acknowledge bit followed by a stop condition. Figure 7 shows how the internal register address maintained by the AR0234CS is loaded and incremented as the sequence proceeds.

Figure 7. Single READ from Random Location

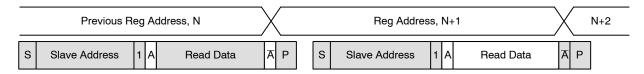

## **Single READ from Current Location**

This sequence (Figure 8) performs a read using the current value of the AR0234CS internal register address.

The master terminates the READ by generating a no-acknowledge bit followed by a stop condition. The figure shows two independent READ sequences.

Figure 8. Single READ from Current Location

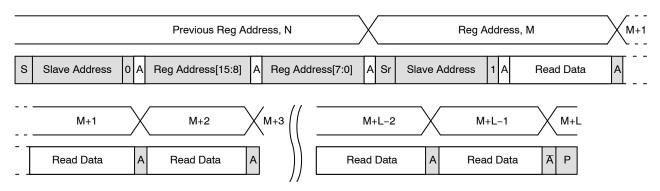

## Sequential READ, Start from Random Location

This sequence (Figure 9) starts in the same way as the single READ from random location (Figure 7). Instead of generating a no-acknowledge bit after the first byte of data

has been transferred, the master generates an acknowledge bit and continues to perform byte READs until "L" bytes have been read.

Figure 9. Sequential READ, Start from Random Location

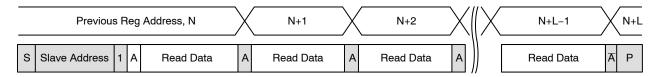

#### Sequential READ, Start from Current Location

This sequence (Figure 10) starts in the same way as the single READ from current location (Figure 8). Instead of generating a no-acknowledge bit after the first byte of data

has been transferred, the master generates an acknowledge bit and continues to perform byte READs until "L" bytes have been read.

Figure 10. Sequential READ, Start from Current Location

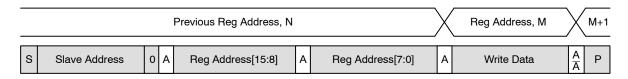

#### Single WRITE to Random Location

This sequence (Figure 11) begins with the master generating a start condition. The slave address/data direction byte signals a WRITE and is followed by the HIGH

then LOW bytes of the register address that is to be written. The master follows this with the byte of write data. The WRITE is terminated by the master generating a stop condition.

Figure 11. Single WRITE to Random Location

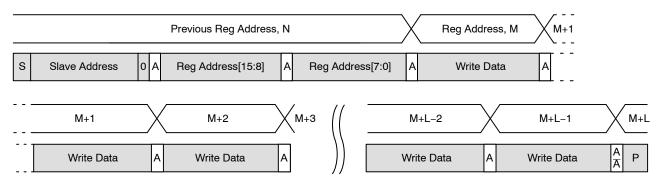

## Sequential WRITE, Start at Random Location

This sequence (Figure 12) starts in the same way as the single WRITE to random location (Figure 11). Instead of generating a no-acknowledge bit after the first byte of data

has been transferred, the master generates an acknowledge bit and continues to perform byte WRITEs until "L" bytes have been written. The WRITE is terminated by the master generating a stop condition.

Figure 12. Sequential WRITE, Start at Random Location

#### **ELECTRICAL SPECIFICATIONS**

PIXCLK Frequency = 90 MHz;

MIPI off.

Unless otherwise stated, the following specifications apply to the following conditions:

$$\begin{split} &V_{DD}=V_{DD}\_PHY=V_{DD}\_DATA=1.2~V~\pm0.06;\\ &V_{DD}\_IO=V_{AA}=V_{AA}\_PIX=2.8~V~\pm0.3~V;~V_{DDIO}\_PHY=1.8~V~\pm0.1~V\\ &T_A=-40^{\circ}C~to~+85^{\circ}C;\\ &Output~Load=10~pF; \end{split}$$

## Two-Wire Serial Register Interface

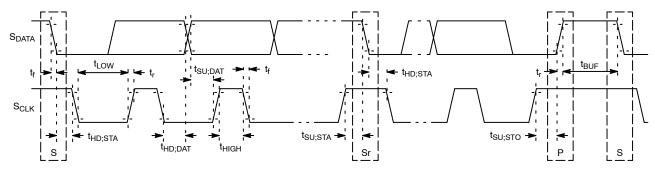

The electrical characteristics of the two–wire serial register interface ( $S_{CLK}$ ,  $S_{DATA}$ ) are shown in Figure 13 and Table 4.

NOTE: Read sequence: For an 8-bit READ, read waveforms start after WRITE command and register address are issued.

Figure 13. Two-Wire Serial Bus Timing Parameters

## Table 4. TWO-WIRE SERIAL BUS CHARACTERISTICS

$(f_{EXTCLK} = 27 \text{ MHz}; V_{DD} = 1.2 \text{ V}; V_{DD\_IO} = 2.8 \text{ V}; V_{AA} = 2.8 \text{ V}; V_{AA\_PIX} = 2.8 \text{ V}; V_{DD\_PHY} = 1.2 \text{ V}; V_{DDIO\_PHY} = 1.8 \text{ V}; T_{A} = 25^{\circ}\text{C})$

|                                                                                                    |                     | Standard Mode |               | Fast-                  | Mode         |      |

|----------------------------------------------------------------------------------------------------|---------------------|---------------|---------------|------------------------|--------------|------|

| Parameter                                                                                          | Symbol              | Min           | Max           | Min                    | Max          | Unit |

| S <sub>CLK</sub> Clock Frequency                                                                   | f <sub>SCL</sub>    | 0             | 100           | 0                      | 400          | kHz  |

| Hold Time (Repeated) START<br>Condition (After This Period, the<br>First Clock Pulse is Generated) | t <sub>HD;STA</sub> | 4.0           | -             | 0.6                    | -            | μs   |

| LOW Period of the S <sub>CLK</sub> Clock                                                           | t <sub>LOW</sub>    | 4.7           | -             | 1.3                    | -            | μs   |

| HIGH Period of the S <sub>CLK</sub> Clock                                                          | tнідн               | 4.0           | -             | 0.6                    | -            | μs   |

| Set-up Time for a Repeated<br>START Condition                                                      | tsu;sta             | 4.7           | -             | 0.6                    | -            | μs   |

| Data Hold Time                                                                                     | t <sub>HD;DAT</sub> | 0 (Note 4)    | 3.45 (Note 5) | 0 (Note 6)             | 0.9 (Note 5) | μs   |

| Data Set-up Time                                                                                   | t <sub>SU;DAT</sub> | 250           | -             | 100 (Note 6)           | -            | ns   |

| Rise Time of both S <sub>DATA</sub> and S <sub>CLK</sub> Signals                                   | t <sub>r</sub>      | -             | 1000          | 20 + 0.1Cb<br>(Note 7) | 300          | ns   |

| Fall Time of both S <sub>DATA</sub> and S <sub>CLK</sub> Signals                                   | t <sub>f</sub>      | -             | 300           | 20 + 0.1Cb<br>(Note 7) | 300          | ns   |

| Set-up Time for STOP Condition                                                                     | t <sub>SU;STO</sub> | 4.0           | -             | 0.6                    | -            | μs   |

| Bus Free Time between a STOP and START Condition                                                   | t <sub>BUF</sub>    | 4.7           | -             | 1.3                    | -            | μs   |

| Capacitive Load for each Bus Line                                                                  | Cb                  | -             | 400           | -                      | 400          | pF   |

#### Table 4. TWO-WIRE SERIAL BUS CHARACTERISTICS (continued)

(f<sub>EXTCLK</sub> = 27 MHz; V<sub>DD</sub> = 1.2 V; V<sub>DD</sub>\_IO = 2.8 V; V<sub>AA</sub> = 2.8 V; V<sub>AA</sub>\_PIX = 2.8 V; V<sub>DD</sub>\_PHY = 1.2 V; V<sub>DDIO</sub>\_PHY = 1.8 V; T<sub>A</sub> = 25°C)

|                                           |          | Standard Mode |     | Fast-Mode |     |      |

|-------------------------------------------|----------|---------------|-----|-----------|-----|------|

| Parameter                                 | Symbol   | Min           | Max | Min       | Max | Unit |

| Serial Interface Input Pin<br>Capacitance | CIN_SI   | -             | 3.3 | -         | 3.3 | pF   |

| S <sub>DATA</sub> Max Load Capacitance    | CLOAD_SD | -             | 30  | -         | 30  | pF   |

| S <sub>DATA</sub> Pull-up Resistor        | RSD      | 1.5           | 4.7 | 1.5       | 4.7 | kΩ   |

- 1. This table is based on I<sup>2</sup>C standard (v2.1 January 2000). Philips Semiconductor.

- 2. Two-wire control is I<sup>2</sup>C-compatible.

- 3. All values referred to  $V_{IHmin}$  = 0.9  $V_{DD}$ IO and  $V_{ILmax}$  = 0.1  $V_{DD}$ IO levels. Sensor EXCLK = 27 MHz.

- 4. A device must internally provide a hold time of at least 300 ns for the SDATA signal to bridge the undefined region of the falling edge of SCLK. The two-wire standard specifies a minimum rise and fall time for Fast-Mode operation. This specification is not a timing requirement that is enforced on ON Semiconductor sensor's as a receiver, because our receivers are designed to work in mixed systems with std-mode where no such minimum rise and fall times are required/specified. However, it's the host's responsibility when using fast edge rates, especially when two-wire slew-rate driver control isn't available, to manage the generated EMI, and the potential voltage undershoot on the sensor receiver circuitry, to avoid activating sensor ESD diodes and current-clamping circuits. This is typically not an issue in most applications, but should be checked if below minimum fall times and rise times are required. A device must internally provide a hold time of at least 300 ns for the S<sub>DATA</sub> signal to bridge the undefined region of the falling edge of S<sub>CLK</sub>.

- 5. The maximum t<sub>HD:DAT</sub> has only to be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the S<sub>CLK</sub> signal.

- 6. A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU:DAT</sub> 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the S<sub>CLK</sub> signal. If such a device does stretch the LOW period of the S<sub>CLK</sub> signal, it must output the next data bit to the S<sub>DATA</sub> line t<sub>r</sub> max + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the S<sub>CLK</sub> line is released.

- 7. Cb = total capacitance of one bus line in pF.

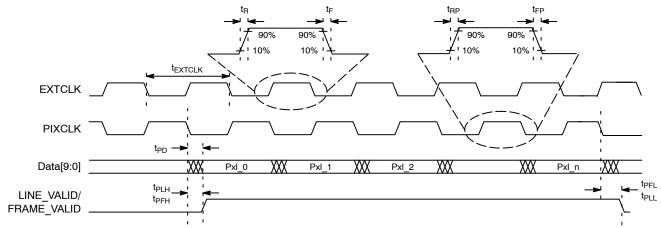

#### I/O Timing

By default, the AR0234CS launches pixel data, FV and LV with the falling edge of PIXCLK. The expectation is that the user captures D<sub>OUT</sub>[9:0], FV and LV using the rising

edge of PIXCLK. The launch edge of PIXCLK can be configured in register R0x3028. See Figure 14 and Table 5 for I/O timing (AC) characteristics.

Figure 14. I/O Timing Diagram

Table 5. I/O TIMING CHARACTERISTICS, PARALLEL OUTPUT (1.8 V V<sub>DD</sub>\_IO) (Note 8)

| Symbol              | Definition                            | Condition                                               | Min  | Тур | Max   | Unit |

|---------------------|---------------------------------------|---------------------------------------------------------|------|-----|-------|------|

| f <sub>EXTCLK</sub> | Input Clock Frequency                 |                                                         | 6    | -   | 54    | MHz  |

| t <sub>EXTCLK</sub> | Input Clock Period                    |                                                         | 18.5 | -   | 166.7 | ns   |

| t <sub>R</sub>      | Input Clock Rise Time                 | PLL Enabled                                             | -    | 3   | -     | ns   |

| t <sub>F</sub>      | Input Clock Fall Time                 | PLL Enabled                                             | -    | 3   | -     | ns   |

| t <sub>JITTER</sub> | Input Clock Jitter                    |                                                         | -    | -   | 600   | ns   |

| t <sub>cp</sub>     | EXTCLK to PIXCLK<br>Propagation Delay | Nominal Voltages, PLL Disabled,<br>PIXCLK Slew Rate = 4 | 9    | _   | 106   | ns   |

| t <sub>RP</sub>     | PIXCLK Rise Time                      | PCLK Slew Rate = 6                                      | 2.1  | -   | 4.2   | ns   |

| t <sub>FP</sub>     | PIXCLK Fall Time                      | PCLK Slew Rate = 6                                      | 1    | -   | 2.7   | ns   |

|                     | PIXCLK Duty Cycle                     |                                                         | 30   | -   | 55    | %    |

| f <sub>PIXCLK</sub> | PIXCLK Frequency                      | PIXCLK Slew Rate = 6, Data Slew Rate = 7                | 6    | -   | 90    | MHz  |

| t <sub>PD</sub>     | PIXCLK to Data Valid                  | PIXCLK Slew Rate = 6, Data Slew Rate = 7                | 2.5  | =   | 3.6   | ns   |

| t <sub>PFH</sub>    | PIXCLK to FV HIGH                     | PIXCLK Slew Rate = 6, Data Slew Rate = 7                | 2.5  | -   | 3.0   | ns   |

| t <sub>PLH</sub>    | PIXCLK to LV HIGH                     | PIXCLK Slew Rate = 6, Data Slew Rate = 7                | 2.2  | -   | 3.0   | ns   |

| t <sub>PFL</sub>    | PIXCLK to FV LOW                      | PIXCLK Slew Rate = 6, Data Slew Rate = 7                | 0.5  | -   | 1.2   | ns   |

| t <sub>PLL</sub>    | PIXCLK to LV LOW                      | PIXCLK Slew Rate = 6, Data Slew Rate = 7                | 0.2  | -   | 0.7   | ns   |

| C <sub>IN</sub>     | Input Pin Capacitance                 |                                                         | -    | 2.5 | -     | pF   |

<sup>8.</sup> Minimum and maximum values are taken at 105°C ambient, 1.7 V and -40°C ambient, 1.9 V. All values are taken at the 50% transition point. The loading used is 10 pF.

Table 6. I/O TIMING CHARACTERISTICS, PARALLEL OUTPUT (2.8 V  $V_{DD}$ \_IO) (Note 10)

| Symbol              | Definition                            | Condition                                            | Min  | Тур | Max   | Unit |

|---------------------|---------------------------------------|------------------------------------------------------|------|-----|-------|------|

| f <sub>EXTCLK</sub> | Input Clock Frequency                 |                                                      | 6    | -   | 54    | MHz  |

| t <sub>EXTCLK</sub> | Input Clock Period                    |                                                      | 18.5 | -   | 166.7 | ns   |

| t <sub>R</sub>      | Input Clock Rise Time                 | PLL Enabled                                          | -    | 3   | -     | ns   |

| t <sub>F</sub>      | Input Clock Fall Time                 | PLL Enabled                                          | -    | 3   | -     | ns   |

| UITTER              | Input Clock Jitter                    | Nominal Voltages, PLL Disabled, PIXCLK Slew Rate = 4 | -    | -   | 600   | ns   |

| t <sub>cp</sub>     | EXTCLK to PIXCLK<br>Propagation Delay | Nominal Voltages, PLL Disabled, PIXCLK Slew Rate = 4 | 4.3  | -   | 105   | ns   |

| t <sub>RP</sub>     | PIXCLK Rise Time                      | PCLK Slew Rate = 6                                   | 0.9  | _   | 2.3   | ns   |

| t <sub>FP</sub>     | PIXCLK Fall Time                      | PCLK slew rate = 6                                   | 0.5  | _   | 1.5   | ns   |

|                     | PIXCLK Duty Cycle                     |                                                      | 40   | _   | 55    | %    |

| f <sub>PIXCLK</sub> | PIXCLK Frequency                      | PIXCLK Slew Rate = 6, Data Slew Rate = 7             | 6    | -   | 90    | MHz  |

| t <sub>PD</sub>     | PIXCLK to Data Valid                  | PIXCLK Slew Rate = 6, Data Slew Rate = 7             | 2.2  | _   | 3.1   | ns   |

| t <sub>PFH</sub>    | PIXCLK to FV HIGH                     | PIXCLK Slew Rate = 6, Data Slew Rate = 7             | 1.7  | -   | 2.4   | ns   |

| t <sub>PLH</sub>    | PIXCLK to LV HIGH                     | PIXCLK Slew Rate = 6, Data Slew Rate = 7             | 1.7  | -   | 2.3   | ns   |

| t <sub>PFL</sub>    | PIXCLK to FV LOW                      | PIXCLK Slew Rate = 6, Data Slew Rate = 7             | 0.8  | _   | 1.1   | ns   |

| t <sub>PLL</sub>    | PIXCLK to LV LOW                      | PIXCLK Slew Rate = 6, Data Slew Rate = 7             | 0.4  | -   | 0.9   | ns   |

| C <sub>IN</sub>     | Input Pin Capacitance                 |                                                      | -    | 2.5 | -     | pF   |

<sup>10.</sup> Minimum and maximum values are taken at 105°C ambient, 1.7 V and -40°C ambient, 1.9 V. All values are taken at the 50% transition point. The loading used is 10 pF.

<sup>9.</sup> Jitter from PIXCLK is already taken into account in the data for all of the output parameters.

<sup>11.</sup> Jitter from PIXCLK is already taken into account in the data for all of the output parameters.

Table 7. I/O RISE SLEW RATE (2.8 V V<sub>DD</sub>\_IO) (Note 12)

| Parallel Slew (R0x306E[15:13]) | Min  | Тур | Max  | Unit |

|--------------------------------|------|-----|------|------|

| 0                              | 0.39 |     | 0.91 | V/ns |

| 1                              | 0.49 |     | 1.85 | V/ns |

| 2                              | 0.54 |     | 2.14 | V/ns |

| 3                              | 0.64 |     | 2.30 | V/ns |

| 4                              | 0.80 |     | 2.45 | V/ns |

| 5                              | 1.00 |     | 2.79 | V/ns |

| 6                              | 1.13 |     | 3.06 | V/ns |

| 7                              | 1.27 |     | 3.33 | V/ns |

<sup>12.</sup> Minimum and maximum values are taken at 105°C ambient, 2.5 V and -40°C junction, 3.1 V. The loading used is 10 pF.

Table 8. I/O FALL SLEW RATE (2.8 V V<sub>DD</sub>\_IO) (Note 13)

| Parallel Slew (R0x306E[15:13]) | Min  | Тур | Max  | Unit |

|--------------------------------|------|-----|------|------|

| 0                              | 0.37 |     | 2.66 | V/ns |

| 1                              | 0.54 |     | 3.15 | V/ns |

| 2                              | 0.67 |     | 3.52 | V/ns |

| 3                              | 1.25 |     | 3.90 | V/ns |

| 4                              | 1.55 |     | 4.03 | V/ns |

| 5                              | 1.77 |     | 4.15 | V/ns |

| 6                              | 1.94 |     | 4.21 | V/ns |

| 7                              | 2.07 |     | 4.21 | V/ns |

<sup>13.</sup> Minimum and maximum values are taken at 105°C ambient, 1.7 V and -40°C ambient, 1.9 V. The loading used is 10 pF.

Table 9. I/O RISE SLEW RATE (1.8 V  $V_{DD}$ \_IO) (Note 14)

| Parallel Slew (R0x306E[15:13]) | Min  | Тур | Max  | Unit |

|--------------------------------|------|-----|------|------|

| 0                              | 0.19 |     | 0.31 | V/ns |

| 1                              | 0.22 |     | 0.33 | V/ns |

| 2                              | 0.24 |     | 0.38 | V/ns |

| 3                              | 0.27 |     | 0.64 | V/ns |

| 4                              | 0.29 |     | 0.76 | V/ns |

| 5                              | 0.32 |     | 0.85 | V/ns |

| 6                              | 0.34 |     | 0.91 | V/ns |

| 7                              | 0.37 |     | 0.97 | V/ns |

<sup>14.</sup> Minimum and maximum values are taken at 105°C ambient, 1.7 V and -40°C ambient, 1.9 V. The loading used is 10 pF.

Table 10. I/O FALL SLEW RATE (1.8 V V<sub>DD</sub>\_IO) (Note 15)

| Parallel Slew (R0x306E[15:13]) | Min  | Тур | Max  | Unit |

|--------------------------------|------|-----|------|------|

| 0                              | 0.17 |     | 0.32 | V/ns |

| 1                              | 0.23 |     | 0.61 | V/ns |

| 2                              | 0.29 |     | 1.13 | V/ns |

| 3                              | 0.32 |     | 1.39 | V/ns |

| 4                              | 0.37 |     | 1.55 | V/ns |

| 5                              | 0.43 |     | 1.69 | V/ns |

| 6                              | 0.50 |     | 1.80 | V/ns |

| 7                              | 0.61 |     | 1.99 | V/ns |

<sup>15.</sup> Minimum and maximum values are taken at 105°C ambient, 1.7 V and -40°C ambient, 1.9 V. The loading used is 10 pF.

#### **DC Electrical Characteristics**

The DC electrical characteristics are shown in Table 11, Table 12, Table 13, and Table 14.

**Table 11. DC ELECTRICAL CHARACTERISTICS**

| Symbol                  | Definition            | Condition                                 | Min                       | Тур     | Max                    | Slew Rate | Unit |

|-------------------------|-----------------------|-------------------------------------------|---------------------------|---------|------------------------|-----------|------|

| $V_{DD}$                | Core Digital Voltage  |                                           | 1.14                      | 1.2     | 1.26                   |           | V    |

| V <sub>DD</sub> _IO     | I/O Digital Voltage   |                                           | 1.7/2.5                   | 1.8/2.8 | 1.9/3.1                |           | V    |

| V <sub>DD</sub> _IO_PHY | I/O Power Supply      |                                           | 1.7                       | 1.8     | 1.9                    |           | V    |

| V <sub>AA</sub>         | Analog Voltage        |                                           | 2.5                       | 2.8     | 3.1                    |           | V    |

| V <sub>AA</sub> _PIX    | Pixel Supply Voltage  |                                           | 2.5                       | 2.8     | 3.1                    |           | V    |

| V <sub>DD</sub> _PHY    | MIPI Supply Voltage   |                                           | 1.14                      | 1.2     | 1.26                   |           | V    |

| V <sub>DD</sub> _DATA   | MIPI Supply Voltage   |                                           | 1.14                      | 1.2     | 1.26                   |           | V    |

| V <sub>AA</sub> _PHY    | MIPI Supply Voltage   |                                           | 2.5                       | 2.8     | 3.1                    |           | V    |

| V <sub>IH</sub>         | Input HIGH Voltage    |                                           | VDD_IO *<br>0.7           | -       | _                      |           | V    |

| V <sub>IL</sub>         | Input LOW Voltage     |                                           | -                         | -       | VDD_IO *<br>0.3        |           | V    |

| I <sub>IN</sub>         | Input Leakage Current | No Pull-up Resistor; VIN = VDD_IO or DGND |                           | -       | 20                     |           | uA   |

| V <sub>OH</sub>         | Output HIGH Voltage   |                                           | VDD_IO *<br>0.7 (1.8/2.8) | -       | -                      | 0         | V    |

| V <sub>OH</sub>         | Output HIGH Voltage   |                                           | VDD_IO *<br>0.7 (1.8/2.8) | -       | -                      | 7         | V    |

| V <sub>OL</sub>         | Output LOW Voltage    |                                           | _                         | -       | 0.4<br>(1.8 V/2.8 V)   | 0         | V    |

| V <sub>OL</sub>         | Output LOW Voltage    | VDD_IO = 2.8 V                            | _                         | -       | 0.4<br>(1.8 V/2.8 V)   | 7         | V    |

| I <sub>OH</sub>         | Output HIGH Current   | At Specified VOH                          | -                         | -       | 3<br>(1.8 V/2.8 V)     | 0         | mA   |

| I <sub>OH</sub>         | Output HIGH Current   | At Specified VOH                          |                           | -       | 7 (1.8 V)<br>12(2.8 V) | 7         | mA   |

| I <sub>OL</sub>         | Output LOW Current    | At Specified VOL                          | -                         | -       | 2 (1.8 V)<br>3(2.8 V)  | 0         | mA   |

| I <sub>OL</sub>         | Output LOW Current    | At Specified VOL                          | -                         | -       | 7 (1.8 V)<br>9(2.8 V)  | 7         | mA   |

**CAUTION:** Stresses greater than those listed in Table 12 may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

**Table 12. ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Parameter                           | Min  | Max                      | Unit |

|---------------------|-------------------------------------|------|--------------------------|------|

| V <sub>SUPPLY</sub> | Power Supply Voltage (All Supplies) | -0.3 | 4.5                      | V    |

| I <sub>SUPPLY</sub> | Total Power Supply Current          | -    | 400                      | mA   |

| I <sub>GND</sub>    | Total Ground Current                | -    | 400                      | mA   |

| V <sub>IN</sub>     | DC Input Voltage                    | -0.3 | V <sub>DD</sub> IO + 0.3 | V    |

| V <sub>OUT</sub>    | DC Output Voltage                   | -0.3 | V <sub>DD</sub> IO + 0.3 | V    |

| T <sub>STG</sub>    | Storage Temperature (Note 16)       | -40  | +125                     | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>16.</sup> Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### Table 13. OPERATING CURRENT CONSUMPTION FOR PARALLEL OUTPUT

$(V_{AA} = V_{AA}\_PIX = V_{DD}\_IO = V_{AA}\_PHY = 2.8 \text{ V}; V_{DD} = V_{DD}\_PHY = V_{DD}\_DATA = 1.2 \text{ V}; V_{DDIO}\_PHY = 1.8 \text{ V}; PLL Enabled and PIXCLK = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; V_{DDIO}\_PHY = 1.8 V; PLL Enabled = 1.2 V; PLL E$ = 90 MHz;  $T_A = 25^{\circ}C$ ;  $C_{LOAD} = 10 pF$ )

| Symbol                         | Parameter                         | Condition                                   | Min | Тур | Max | Unit |

|--------------------------------|-----------------------------------|---------------------------------------------|-----|-----|-----|------|

| IDD_PHY +<br>IDD_DATA +<br>IDD | Digital Operating Current         | Parallel, Streaming, Full Resolution 30 fps | -   | 52  | 105 | mA   |

| IDD_IO                         | I/O Digital Operating Current     | Parallel, Streaming, Full Resolution 30 fps | -   | 40  | 112 | mA   |

| IDDIO_PHY                      | I/O PHY Digital Operating Current | Parallel, Streaming, Full Resolution 30 fps | -   | 0   | 1   | mA   |

| IAA_PHY +<br>IAA               | Analog Operating Current          | Parallel, Streaming, Full Resolution 30 fps | -   | 50  | 90  | mA   |

| IAA_PIX                        | Pixel Supply Current              | Parallel, Streaming, Full Resolution 30 fps | -   | 5   | 13  | mA   |

<sup>17.</sup> Values in Table 13 are subject to change.

3.  $V_{AA}$ ,  $\overline{V}_{AA}$ PHY and  $\overline{V}_{AA}$ PIX

## Table 14. OPERATING CURRENT CONSUMPTION FOR MIPI OUTPUT

$(V_{AA} = V_{AA}\_PIX = V_{DD}\_IO = V_{AA}\_PHY = 2.8 \text{ V}; V_{DD} = V_{DD}\_PHY = V_{DD}\_DATA = 1.2 \text{ V}; V_{DDIO}\_PHY = 1.8 \text{ V}; PLL Enabled and PIXCLK = 1.2 \text{ V}; V_{DDIO}\_PHY = 1.8 \text{ V}; PLL Enabled and PIXCLK = 1.2 \text{ V}; PLL Enabled an$ 90 MHz;  $T_A = 25^{\circ}C$ ;  $C_{LOAD} = 10 \text{ pF}$ )

| Symbol                         | Parameter                         | Condition                                | Min | Тур | Max | Unit |

|--------------------------------|-----------------------------------|------------------------------------------|-----|-----|-----|------|

| IDD_PHY +<br>IDD_DATA +<br>IDD | Digital Operating Current         | MIPI, Streaming, Full Resolution 120 fps | -   | 155 | 250 | mA   |

| IDD_IO                         | I/O Digital Operating Current     | MIPI, Streaming, Full Resolution 120 fps | -   | 0.2 | 1   | mA   |

| IDDIO_PHY                      | I/O PHY Digital Operating Current | MIPI, Streaming, Full Resolution 120 fps | -   | 10  | 12  | mA   |

| IAA_PHY+<br>IAA                | Analog Operating Current          | MIPI, Streaming, Full Resolution 120 fps | -   | 55  | 102 | mA   |

| IAA_PIX                        | Pixel Supply Current              | MIPI, Streaming, Full Resolution 120 fps | -   | 5   | 13  | mA   |

<sup>20.</sup> Values in Table 14 are subject to change.

## **Table 15. STANDBY CURRENT CONSUMPTION**

$(Analog = V_{AA} + V_{AA}PIX + V_{AA}PHY; Digital = V_{DD} + V_{DD}O + V_{DD}PHY + V_{DDIO}PHY + V_{DD}DATA; T_A = 25^{\circ}C)$

| Definition                               | Condition                     | Min | Тур  | MAX   | Unit |

|------------------------------------------|-------------------------------|-----|------|-------|------|

| Soft Standby (Clock Off, Driven Low)     | Analog, 2.8 V                 | -   | 5    | 35    | μΑ   |

|                                          | Digital,<br>1.2 V/1.8 V/2.8 V | -   | 250  | 4000  | μΑ   |

| Soft Standby (Clock On, EXTCLK = 27 MHz) | Analog, 2.8 V                 | -   | 5    | 35    | μΑ   |

|                                          | Digital,<br>1.2 V/1.8 V/2.8 V | -   | 5000 | 14000 | μΑ   |

| nRESET Low (Clk off)                     | Analog, 2.8 V                 | -   | 5    | 35    | μΑ   |

|                                          | Digital,<br>1.2 V/1.8 V/2.8 V | -   | 250  | 4000  | μΑ   |

| nRESET Low                               | Analog, 2.8V                  | -   | 5    | 35    | μΑ   |

|                                          | Digital,<br>1.2 V/1.8 V/2.8 V | -   | 250  | 4000  | μΑ   |

<sup>22.</sup> Values in Table 15 are subject to change.

<sup>18.</sup> Maximum values for V<sub>DD</sub> IO parallel are dependent on the specific load being applied in the final design. Typical values are based on a load of 20 pF.

<sup>19.</sup> The following supply rails can be connected together.

<sup>1.</sup> V<sub>DD</sub>, V<sub>DD</sub>-PHY and V<sub>DD</sub>\_DATA 2. VDD\_IO and VDDIO\_PHY if 1.8 VDC each

<sup>21.</sup> The following supply rails can be connected together.

<sup>1.</sup> V<sub>DD</sub>, V<sub>DD</sub>-PHY and V<sub>DD</sub>\_DATA

2. VDD\_IO and VDDIO\_PHY if 1.8 VDC each

<sup>3.</sup>  $V_{AA}, \overline{V}_{AA}\_PHY$  and  $\overline{V}_{AA}\_PIX$

## **MIPI Electrical Specifications**

The ON Semiconductor AR0234CS sensor supports four lanes of MIPI data.

Compliant to MIPI standards:

- MIPI Alliance Standard for CSI-2 version 1.2

- MIPI Alliance Standard for D-PHY version 1.0

## **MIPI AC and DC Electrical Characteristics**

## Table 16. MIPI HIGH-SPEED TRANSMITTER DC CHARACTERISTICS

| Symbol                    | Parameter                                                                  | Min | Тур | Max  | Unit |

|---------------------------|----------------------------------------------------------------------------|-----|-----|------|------|

| V <sub>OD</sub>           | HS transmit differential voltage                                           | 140 | _   | 270  | mV   |

| V <sub>CMTX</sub>         | HS transmit static common mode voltage                                     | 150 | _   | 250  | mV   |

| $\Delta$ V <sub>OD</sub>  | V <sub>OD</sub> mismatch when output is Differential-1 or Differential-0   | -   | _   | 14   | mV   |

| Δ V <sub>CMTX</sub> (1,0) | V <sub>CMTX</sub> mismatch when output is Differential-1 or Differential-0 | -   | _   | 5    | mV   |

| V <sub>OHHS</sub>         | HS output HIGH voltage                                                     | -   | _   | 360  | mV   |

| Z <sub>OS</sub>           | Single-ended output impedance                                              | 40  | _   | 62.5 | Ω    |

| Δ Z <sub>OS</sub>         | Single-ended output impedance mismatch                                     | -   | =   | 10   | %    |

#### Table 17. MIPI HIGH-SPEED TRANSMITTER AC CHARACTERISTICS

| Symbol            | Parameter        | Min | Тур | Max | Unit |

|-------------------|------------------|-----|-----|-----|------|

|                   | Data bit rate    | _   | _   | 768 | Mb/s |

| t <sub>rise</sub> | 20–80% rise time | 150 | _   | 160 | ps   |

| t <sub>fall</sub> | 20-80% fall time | 150 | 1   | 160 | ps   |

#### Table 18. MIPI LOW-POWER TRANSMITTER DC CHARACTERISTICS

| Symbol           | Parameter                          | Min | Тур  | Max | Unit |

|------------------|------------------------------------|-----|------|-----|------|

| V <sub>OL</sub>  | Thevenin output low level          | 1   | -    | 50  | mV   |

| V <sub>OH</sub>  | Thevenin output high level         | 1.1 | 1.15 | 1.3 | V    |

| Z <sub>OLP</sub> | Output impedance of LP transmitter | 110 | =    | =   |      |

## Table 19. MIPI LOW-POWER TRANSMITTER AC CHARACTERISTICS

| Symbol            | Parameter                              | Min | Тур | Max | Unit  |

|-------------------|----------------------------------------|-----|-----|-----|-------|

| t <sub>rise</sub> | 15–85% rise time                       | _   | _   | 25  | ns    |

| t <sub>fall</sub> | 15-85% fall time                       | =   | =   | 25  | ns    |

| Slew              | Slew rate (C <sub>LOAD</sub> 5–20 pf)  | =   | =   | 250 | mV/ns |

| Slew              | Slew rate (C <sub>LOAD</sub> 20–70 pf) | -   | -   | 150 | mV/ns |

#### **POWER-ON RESET AND STANDBY TIMING**

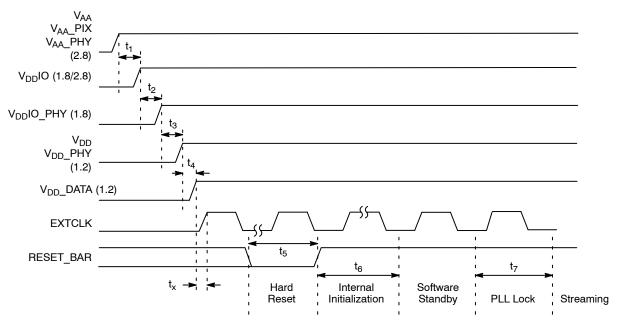

#### **Power-Up Sequence**

The recommended power-up sequence for the AR0234 is shown in Figure 15. The available power supplies ( $V_{AA}/V_{AA}$ \_PIX/ $V_{AA}$ \_PHY,  $V_{DD}IO$ ,  $V_{DD}IO$ \_PHY,  $V_{DD}/V_{DD}$ \_PHY, and  $V_{DD}$ \_DATA) must have the separation specified below.

- 1. Turn on  $V_{AA}/V_{AA}$ \_PIX/ $V_{AA}$ \_PHY power supply.

- 2. After 100  $\mu$ s, turn on  $V_{DD}IO$  power supply.

- After 100 μs, turn on V<sub>DD</sub>IO\_PHY(1.8 V) power supply.

- 4. After 100  $\mu$ s, turn on  $V_{DD}/V_{DD}$ \_PHY power supply

- 5. After 100 μs, turn on V<sub>DD</sub> DATA power supply.

- 6. After the last power supply is stable, enable EXTCLK.

- 7. Assert RESET\_N for at least 1 ms. The parallel interface will be tri-stated during this time.

- 8. Wait for ~160000 EXTCLKs for internal initialization into soft standby where M3ROM and full OTPM upload would be complete.

- 9. Set streaming mode (mode\_select/stream (R0x301A[2]) = 1) and the internal PLL would be enabled (not locked yet).

- 10. Wait for 1 ms for PLL lock to complete, Part will then go into streaming mode.

Figure 15. Power-up Sequence

## **Table 20. POWER-UP SEQUENCE**

| SN | Definition                                                                       | Symbol         | Min    | Тур   | Max | Unit   |

|----|----------------------------------------------------------------------------------|----------------|--------|-------|-----|--------|

| 1  | V <sub>AA</sub> /V <sub>AA</sub> _PIX/V <sub>AA</sub> _PHY to V <sub>DD</sub> IO | t <sub>1</sub> | 0      | 100   | _   | μs     |

| 2  | V <sub>DD</sub> IO to V <sub>DD</sub> IO_PHY                                     | t <sub>2</sub> | 0      | 100   | -   | μs     |

| 3  | V <sub>DD</sub> IO_PHY to V <sub>DD</sub> /V <sub>DD</sub> _PHY                  | t <sub>3</sub> | 0      | 100   | _   | μs     |

| 4  | V <sub>DD</sub> /V <sub>DD</sub> PHY to V <sub>DD</sub> DATA                     | t <sub>4</sub> | 0      | 100   | -   | μs     |

| 5  | Xtal Settle Time (Component Dependent)                                           | t <sub>x</sub> | -      | 30 ms | -   | ms     |

| 6  | Hard Reset                                                                       | t <sub>5</sub> | 1      | -     | _   | ms     |

| 7  | Internal Initialization                                                          | t <sub>6</sub> | 160000 | -     | -   | EXTCLK |

| 8  | PLL Lock Time                                                                    | t <sub>7</sub> | 1      | -     | _   | ms     |

<sup>23.</sup> V<sub>DD</sub> and V<sub>DD</sub>\_DATA can be tied together (t<sub>4</sub> becomes '0' in this case).

<sup>24.</sup> VAA/VAAPIX/VAA\_PHY can be tied together.

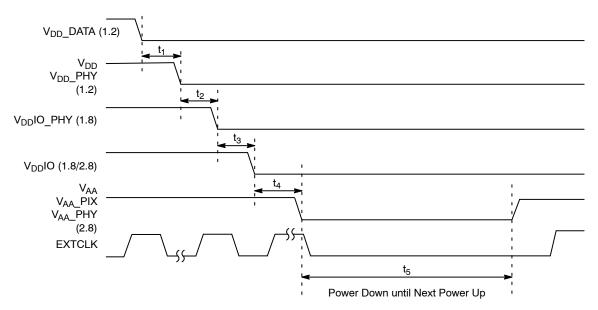

## **Power Down Sequence**

The recommended power-down sequence for the AR0234 is shown in Figure 16. The available power supplies ( $V_{AA}/V_{AA}$ \_PIX/ $V_{AA}$ \_PHY,  $V_{DD}$ IO,  $V_{DD}$ IO\_PHY,  $V_{DD}/V_{DD}$ \_PHY, and  $V_{DD}$ \_DATA) must have the separation specified below.

- 1. Disable streaming if output is active by setting standby R0x301a[2] = 0.

- 2. The soft standby state is reached after the current row or frame, depending on configuration, has ended.

- 3. Turn off V<sub>DD</sub>\_DATA.

- 4. Turn off  $V_{DD}/V_{DD}$  PHY.

- 5. Turn off V<sub>DD</sub>IO\_PHY.

- 6. Turn off V<sub>DD</sub>IO.

- 7. Turn off V<sub>AA</sub>/V<sub>AA</sub>\_PIX/V<sub>AA</sub>\_PHY.

Figure 16. Power-down Sequence

**Table 21. POWER-DOWN SEQUENCE**

| SN | Definition                                                                       | Symbol         | Min | Тур | Max | Unit |

|----|----------------------------------------------------------------------------------|----------------|-----|-----|-----|------|

| 1  | V <sub>DD</sub> _DATA to V <sub>DD</sub> /V <sub>DD</sub> _PHY                   | t <sub>1</sub> | 0   | _   | -   |      |

| 2  | V <sub>DD</sub> /V <sub>DD</sub> PHY to V <sub>DD</sub> IO_PHY                   | t <sub>2</sub> | 0   | -   | -   |      |

| 3  | V <sub>DD</sub> IO_PHY to V <sub>DD</sub> IO                                     | t <sub>3</sub> | 0   | -   | -   |      |

| 4  | V <sub>DD</sub> IO to V <sub>AA</sub> /V <sub>AA</sub> _PIX/V <sub>AA</sub> _PHY | t <sub>4</sub> | 0   | -   | -   |      |

| 5  | PwrDn until Next Pwrup Time                                                      | t <sub>5</sub> | 100 | _   | -   | ms   |

<sup>25.</sup>  $V_{DD}$  and  $V_{DD}$ DATA can be tied together.

<sup>26.</sup> V<sub>AA</sub>/V<sub>AA</sub>PIX/V<sub>AA</sub>PHY can be tied together.

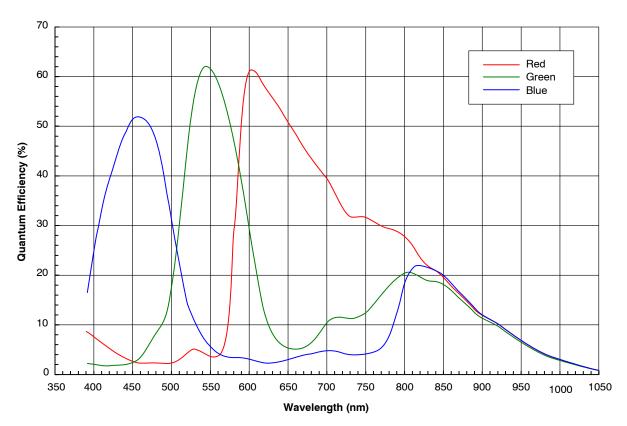

Figure 17. Quantum Efficiency - Color Sensor (Typical)

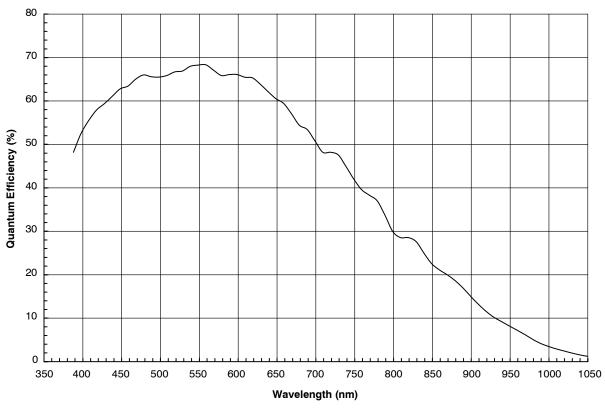

Figure 18. Quantum Efficiency - Monochrome Sensor (Typical)

0

#### ODCSP83 5.595x9.995

CASE 570CK **ISSUE A**

**DATE 16 AUG 2019**

| DOCUMENT NUMBER: | 98AON87372G         | Electronic versions are uncontrolled except when accessed directly from Printed versions are uncontrolled except when stamped "CONTROLLED" |             |

|------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | ODCSP83 5.595x9.995 |                                                                                                                                            | PAGE 1 OF 1 |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

STRATEGY AND SOLDERING DETAILS, PLEASE DOWNLOAD

THE ON SEMICONDUCTOR SOLDERING AND MOUNTING TECHNIQUES REFERENCE MANUAL, SOLDERRM/D.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative